一、前言

希望這篇心得文,能給非四大四中二科的學弟妹一點信心,雖然大家都說ICS組很吃血統很競爭,但我還是想鼓勵學弟妹,想考台大ICS就放手去試試吧!

為了還願,這篇心得文會寫得非常詳細,如果還有疑問可以留言或ptt站內信。

二、個人背景:

風大雨大雲科大電機工程系,系排超過50%,有修過類比相關專題,做到postsim(沒下線),只參加過IC contest初賽。

因為我考統測沒有考上台科,使我大一上非常非常墮落,跟室友們翹課熬夜玩遊戲,導致成績倒數,我都要放棄我自己了。大一那年的寒假,我在家裡思考自己不能這麼廢了,決定早點立下目標,提早選好要走的組別,並努力拉回成績。

三、成績:

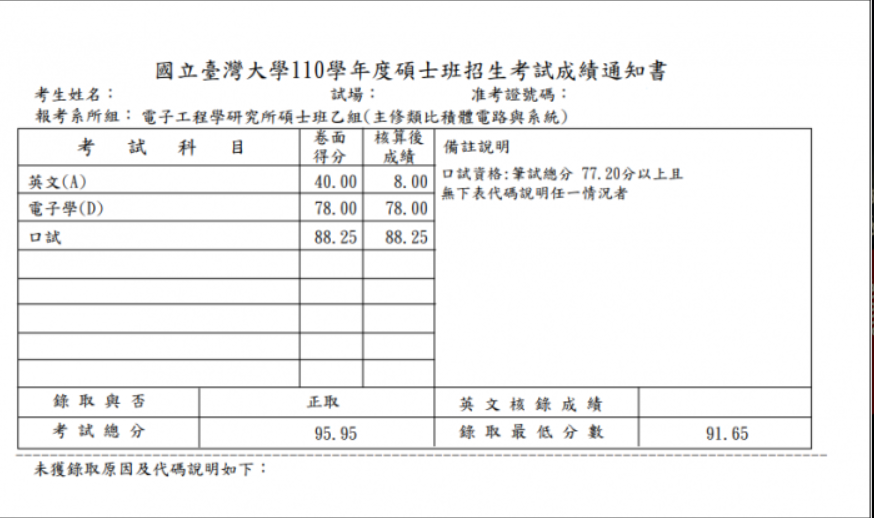

110年台大電子乙(類比ICS組) 正取第6

英文(A) 40

電子學(D) 78

面試 88.25

總分 95.95

台科電子乙二

一階被刷,無面試資格

北科電子丁

電子學考完自信滿滿,但成績發生意外,太丟臉就不放了

四、選組與決定:

修過大一程式設計與大二的組合語言後,我覺得寫程式的過程讓我很痛苦,所以會碰到大量程式的組別完全不考慮。而我在高中時已學過電子學與基本電學,那時對電路設計方面就蠻有興趣的,然後我爬了很多文章並與有相關背景的親戚討論,最後我選擇走類比ICS組。

五、修課狀況:

我在大二時決定走類比ICS,馬上查了電機系與電子系相關IC選修,並計畫好每學期要修哪些課。特別提醒,修相關課程是非常重要的!!以下提供我修過的課給雲科的類比組學弟妹參考,外校生也可以參考課程名稱,對比自己學校開的課。

必修:

●電子學(一)、(二) ●電路學(一)、(二) ●電磁學 ●工數(一)、(二)

IC相關選修:

●類比通訊積體電路設計(碩班)

●類比積體電路分析與設計(一)、(二)

●超大型積體電路設計導論

●高等積體電路應用設計

●積體電路佈局實習

●積體電路實體設計實習

●數位訊號分析與應用

●硬體描述語言設計與模擬(數位IC相關)

●半導體物理(固態組較有關)

大四下修課(很多老師面談會問):

●射頻積體電路特論(碩班)

●類比積體電路設計專論(碩班)

六、參考用書與準備方式

我有報補習班正課與題庫,因為地區關係,看雲端課程比較方便。電子學補年資最深的那位。其實我還為了清大電機丙,補線代、機率,但這兩個科目太花時間了,加上這組書審乘2對我不利,因此我在10月左右決定放棄考台聯,全力讀電子學。所以我主要分享電子學的準備方式。

電子學用書:

1. Microelectronic Circuits 7/e by Sedra, Adel S/ Smith, Kenneth C

2. Microelectronics 2/e by Razavi (看頻率響應章節)

3. 獵殺電子學上、下

4. 原文書習題解答(網路上找到的) 1~11章

5. 微電子學題解(下) By 江昭暟

下一段是時間表,你看完會發現,我看原文書的速度並不快,算很慢了,原因是我花了大量時間在思考觀念,一直想天馬行空的狀況,測試自己的觀念是否扎實,老實說我寫的題目是別人的一半,可能更少。而依照歷屆的台大電子學(D)卷難度,我認為觀念大於解題,歷屆題目很常出現那種你看到後會愣住3分鐘的題型,但是用觀念仔細推敲後,還是能解出來的。

七、時間表

三月~六月: (每天花4小時左右看原文)

拿起Smith原文書從頭開始看,我在看這本書前,幾乎沒認真看過其他原文書,都只有看看公式與圖而已,所以一開始地毯式看過去,很慢是正常的,而且還要翻譯一些名詞,我看一頁大概花15分鐘,後來看習慣後,一頁可以壓縮到5分鐘左右,而且我多益才500,都被我朋友噴很爛,所以不用害怕讀原文書。

六月底時看到第七章偏壓結束。

這時我還有看線代、機率,我把這兩門與電子學的雲端課程排在晚上6點~12點,因為一堂課大概2、3小時,剛好可以看兩部。

一週我讀五天,週四、週日這兩天休息,休息日我就看看劇、約朋友吃飯、玩玩game,我認為一定要安排休息日,讓自己好好放鬆,如果某天狀態不佳或心不在焉,請直接闔上書本去做想做的事,因為我認為這樣讀書效率不好,乾脆別讀。

七月~八月: (10 am ~ 5 pm,約6小時讀Smith)

暑假期間要專題製作,我跟組員大概做了快兩個月才結束,一週有3~4天左右的下午都在忙專題,專題日的晚上看一部雲端課程。沒做專題時就照我上面的時間表讀,晚上看1~2部雲端課程。

兩個月看完Smith第8~12章(差動放大器、頻率響應、迴授與穩定度、輸出級、OPA內部電路),每看完一個章節,當天晚上我就會搭配補習班同樣的章節課程,我覺得搭配看效果很不錯,我再讀原文第二遍時,觀念變更完整。

九月~十二月: (課餘時間讀Smith,每天讀到11點)

一樣一週讀五天,週三、週日休息

大概在11月初將剩下的章節讀完一遍,開始寫獵殺電子學上下冊的後面習題,還有Smith每個章節後面的problems,但Smith我只挑我較不熟的13~17章各15題。上述寫完後開始寫名人堂,寫不熟的單元:迴授穩定度、OP線性電路、CMOS(反向器、邏輯閘)、濾波器、振盪器,其他章節太熟不寫,寫完後覺得差不多了。在十二月底時寫台大98、100學年的考古題,先抓個出題方向。

我看到98年的那題ua741內部,直接傻眼,寫完後沒對答案,我就拿起Smith開始分析ua741(之前跳過這部分),花一整個下午分析完後,突然想起我在高三統測前,拿著課本裡ua741的內部構造跑去問高中的電子學老師這怎麼分析,老師告訴我大學會教(結果沒有XDD),但是我很欣慰自己4年後還是把它分析出來了(雖然是為了考試XD)。

一月~考前: (每天睡到自然醒,醒來看筆記+一天一回考古題,晚上複習完筆記就睡覺)

我將補習班沒上過的Smith冷門電路做了幾頁筆記,ex:濾波器(Tow-thomas biquad、SABs、敏感度、Transconductance-C Filters、Tuning Amp)、單振器(Cross-coupled LC osc)、數位電路(等效負載電容、Driving a Large Capacitance)、Mos速度飽和…等。

因為台大考試範圍是除了元件物理外的全部章節,雖然有些冷門題目歷年完全沒出過,但你怎麼能保證你應考的這年不會出呢?

所以我建議最好是讀到無死角。

題庫班我是跳著看的,將比較特別、沒看過的電路寫成6頁左右的筆記。最後我把正課的筆記做了整理,將原本自己手抄的40多頁(一頁兩面)挑選出我”每天必須複習”的部分(約25頁),再與上述提到的冷門電路筆記、題庫筆記放在一起,總共38頁,考前一個月每天晚上我就複習這38頁,花0.5~1小時左右逐一看過,我很推薦用這個方法,尤其是要準備很多科的考生,這方法能讓你每天花不多時間,就能對某科目保留記憶,並有更多時間分配給其他科目。

這段時間我寫了台大電子學(D)100、103~109,而我覺得 106年、108年偏難,尤其我寫106年寫到崩潰,氣到直接出門喝可樂。108年題目爆多,要選題目寫。而100年、105年偏簡單,今年110年也是,所以我不負責任地預測115年也會很簡單!!

寫完考古題後有些需要補強的觀念,我就會再回去看雲端正課數次,很多部VOD都被我點了1~2次

考試當日:

考卷拿到,我馬上快速的看過每一題,發現跟往年一樣出五、六題大題,每大題都包含數個小題,這些小題每題都5~10分,然後看到最後一大題只有7分,卻有5小題,我果斷判斷如果寫到最後一題只剩20分鐘就往前面檢查,放棄這題。果然到最後只剩15分鐘,我就沒寫了。

今年題目我最有印象的是選擇第一題的e選項,我剛好數位電路部分讀得很深入,有實際推過答案,很開心猜題有猜到。

考完後,我出考場馬上推算自己最高能拿78分,感覺涼了,因為出考場後每個人都在說今年很簡單,加上我不確定自己有沒有計算錯誤。一直到放榜那天,看了成績單,還真的是78分!!也太幸運!!

八、口試:

口試簽到時,發現我這組面試者都是四大四中台科的學生,我整個不寒而慄,覺得危險QQ

第一關(吳安宇教授):

先看了我簡報填的科目成績,說我的必修不太OK喔(我都拿7X~8X),我想說完蛋了壓力測試要來了,然後老師又往右邊看一下類比IC科目成績,驚訝的說:你這個成績怎麼沒推甄阿?

不是阿老師,我就是因為必修分數不高阿XDD

然後問我專題是做什麼?指導老師是誰?

接下來要我回答紙上的3個題目

1.給我看inverter的電路圖與layout圖

吳:如何使fall time與rise time一致?

我:要讓kn=kp

吳:那你layout要怎麼優化?

這時有個插曲,我以為老師說的是在kn=kp的情況下,還要做什麼樣的優化?我心想也太難了吧

我:要加Dummy吧,保持好的電路特性

吳:我不是說這個,你再想一下。

我:(實在想不出來,只好用邏輯推論)如果要讓時間一樣,那un*Cox*(W/L)n必須等於up*Cox*(W/L)p,但電子比電洞的mobility還要快,所以PMOS的寬度要設計的比NMOS的還要大。

吳:你這不是會嗎?說的很好啊

我:抱歉XDDDDD

2.inverter串接inverter的圖

吳:要怎麼設計才能驅動下一級inverter

我:假設第一顆inverter的size是1,第二顆的size是x,那下一顆的size就是x平方,每一顆與下一顆的size乘倍數關係。(Smith第15章的Driving a Large Capacitance)

3.三張FinFET的圖

吳:你會這個嗎?

我:有看過,但不知道原理。

吳:你覺得Source與Drain端在哪裡?(指著第二張圖要我回答)

其實我看到第一張圖有標記腳位XD

於是我就回答是這裡與這裡(指著第二張圖)

吳:你覺得他的寬度跟一般的MOSFET相比,誰比較大?

我:因為它是三維構造,感覺寬度比較大。(這個我不會,講出個道理就行)

第二關(劉深淵教授):

問走類比IC的動機、專題製作的參與比例

白板上畫著主動式負載的差動放大器,輸入為差動訊號

劉:左邊這個MOS的輸入為多少時,可以讓電流源的全部電流流過該MOS

我: √2 *Vov

劉:Vov是什麼?

我: overdrive voltage,當VDS大於等於Vov,電晶體會操作在飽和區

劉:講一下MOS飽和區條件

我:VGS大於Vt,VDS大於等於VOV

劉:offset的定義

我:Vo(dc)/Ad

劉:如何消除offset?

我:差動增益加大

劉:若現在輸入接共模訊號,輸入的上下限是多少?

我:下限是VGS1+電流源的側壓Vov

時間差不多到了,離開前老師誇我程度不錯,然後還問我是不是把全校的IC課程都修完了XDDDDD

第三關(簡韶逸教授)

自我介紹,問「為什麼我們要錄取你?」,我在想因為我是雲科生比較特別吧,我就說了我報考動機,老師很滿意的點頭了。

老師說他是做數位的,要問幾題數位電路

簡:說明inverter的工作原理?

我:根據不同的輸入,PMOS與NMOS會產生對應的五種狀態,使輸出電壓不同。

簡:那如何加速inverter?

主要要加大電流,也就是加大VDD、負載電容小一點,通道寬度加大、溫度降低使mobility變大、改善製程降低Vt

簡:CMOS inverter要如何省電?

我:CMOS的靜態功率為0,動態功率=f*C*VDD^2,所以頻率變小,負載電容要變小,VDD也要小。

簡: (A、B各接反向器,輸出接在一起的邏輯電路) 問我輸出邏輯?

我:A bar + B bar,解釋原理。

第四關(盧信嘉教授)

問專題與修課狀況,專題部分問很細,所以有做專題的話,建議要弄得非常熟。

面試心得:當教授問了你完全沒把握的問題,請你拿出你的邏輯,一句句說出來並慢慢推敲,就算你講錯也沒關係,重點是讓教授知道你有在思考問題,千萬不要卡在那說不會、沒想法。

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

放榜後找教授:

我從放榜當天就上去拜訪各個實驗室了,但發生了一些我沒預料到的事,讓我在找教授的環節上很不順利,第九天才確定了我的指導教授,雖然有些曲折,但跟教授談完後,我還蠻喜歡這個實驗室的,根本繞了一大圈阿啊!!我很期待半年後進入實驗室阿!!

九、結語:

在準備考研的這一年,真的很辛苦,像我到最後只準備一科而已,根本無法想像要考4、5科的同學壓力有多大,考研真的是太可怕了,真心不想再考一次。

很多人都會問說是否該報電子學?我覺得可以補,老師上課的內容足以讓你考台聯、成大、中字輩拿高分,至於如果是考台大,我認為還是要花時間讀Smith的內容會更穩一點。

十、致謝:

首先我要感謝我家人,幫我繳補習班的費用,還有買一張大床,讓我這半年睡得很安穩,我媽到了1月還跟我說考不上可以重考一年XD有夠好笑的!!!然後謝謝哥哥給我面試的意見。

感謝我的考研戰友兼前台科劍道社社長兼死黨,考前兩個月天天跟我一起讀書,平時還糾正我講話的邏輯,讓我在面試時呈現了好的結果,他也正取了想讀的系組。還一直推薦安達充的漫畫給我,安達充萬歲!

感謝我的死黨們,考研時期大家很常一起開視訊聊天,真的很歡樂很放鬆,這一年我都很期待與你們的出遊、群聚,很感謝能擁有你們。

感謝我的五位好朋友,平時我在IG上打一些抒發心情的文,都會勉勵我,支撐我渡過考研低潮期,真的很感謝你們。

謝謝我的ICS組的戰友們,花很多時間與我討論電子學,互相扶持到考前。

感謝我大學專題的指導教授,在面試前幫我看簡報並給我意見,在我到台大找指導教授時,給予我很多想法!!

感謝我的舅舅與表姊夫,給我很多方向與意見,讓我更瞭解IC業界的發展。

感謝碩班學長姊與我一起完成專題的某些細項,並回答我許多專業科目的問題,還給我許多建議。

謝謝在台大電子所的三位雲科學長,我在找指導教授時給予我很多建議與幫助。

感謝分享給我面試經驗的雲科電機同學們

謝謝我的專題組員,幫專題額外做優化、寫專題本,太給力了!!

本文由 Dcard作者 授權轉載